# Fully CMOS-Compatible Integrated Distributed Feedback Laser with 250 °C Fabricated Al<sub>2</sub>O<sub>3</sub>:Er<sup>3+</sup> Gain Medium

Emir Salih Magden<sup>1\*</sup>, Purnawirman<sup>1</sup>, Nanxi Li<sup>1</sup>, Gurpreet Singh<sup>1</sup>, Jonathan D. B. Bradley<sup>1</sup>, Gale S. Petrich<sup>1</sup>, Gerald Leake<sup>2</sup>, Douglas D. Coolbaugh<sup>2</sup>, Michael R. Watts<sup>1</sup>, Leslie A. Kolodziejski<sup>1</sup> <sup>1</sup>Research Laboratory of Electronics, Massachusetts Institute of Technology, 77 Massachusetts Ave., Cambridge, MA 02139, USA <sup>2</sup>College of Nanoscale Science and Engineering, University at Albany, 1400 Washington Ave., Albany, NY 12222, USA \*Corresponding Author: esm@mit.edu

**Abstract:** We demonstrate a DFB laser with a record low temperature (250 °C) fabrication process of low-loss (<0.1 dB/cm) amorphous  $Al_2O_3$ :Er<sup>3+</sup> gain medium by utilizing the substrate bias, facilitating laser integration in a fully CMOS-compatible platform.

OCIS codes: (130.3120) Integrated optics devices; (310.1860) Deposition and fabrication; (140.3500) Lasers, erbium.

## 1. Introduction

The use of Al<sub>2</sub>O<sub>3</sub> doped with rare-earth ions has been studied for integration with CMOS electronics for the past three decades. Aluminum oxide as a host medium has advantages such as higher refractive index than other glasses (silica or phosphate glass), good rare-earth ion solubility, ease of fabrication by physical vapor deposition, and better noise performance than semiconductor amplifiers and lasers [1]. Many on-chip amplifiers, continuous-wave and pulsed lasers with doped Al<sub>2</sub>O<sub>3</sub> have been demonstrated [1-3]. Nevertheless, the most reliable fabrication methods for Al<sub>2</sub>O<sub>3</sub> developed thus far require over 500 °C process temperatures, rendering CMOS integration of the process difficult [4]. Previously, Sedky et al. have shown that post-processing or annealing temperatures over 425 to 525 °C can significantly compromise the integrity of metal contacts by surface oxidization [5]. Furthermore, hour-long exposures to temperatures over 400 °C are known to increase resistance in vias [6], which is detrimental for operation of high-speed active devices such as modulators.

Here, we present a substrate-bias assisted radio frequency (RF) magnetron sputtering process for fabricating lowloss, undoped and rare-earth doped  $Al_2O_3$  films at a temperature as low as 250 °C. We then demonstrate an integrated distributed feedback (DFB) laser, making use of this first fully CMOS-compatible back end process for  $Al_2O_3$ :Er<sup>3+</sup>.

## 2. Material Fabrication and Optimization

We fabricated the  $Al_2O_3:Er^{3+}$  gain medium using a Kurt J. Lesker Lab 18 modular thin film sputtering system with magnetron sputtering guns and RF power supplies. The low base pressure of  $10^{-7}$  Torr, the use of a load lock, the upside-down orientation of the substrate, and separate control of target and substrate shutters during deposition allowed the production of films with consistent quality and thickness.

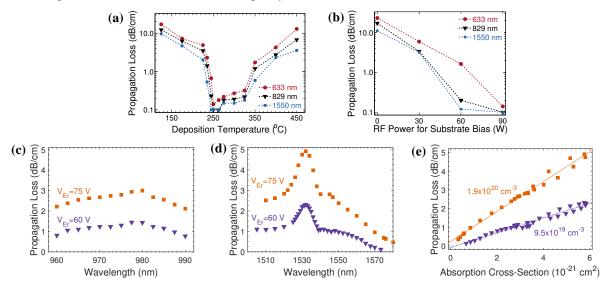

Fig. 1. Process optimization for optical quality of  $Al_2O_3$  films showing propagation loss as a function of (a) deposition temerature, and (b) substrate bias. Absorption measurements around (c) 980 nm and (d) 1550 nm in  $Al_2O_3$ :Er<sup>3+</sup> films with varying bias across the Er target. (e) Er concentrations calculated using the absorption cross-sections in [4], and by taking into account the mode confinement within the gain region.

#### SM1G.2.pdf

First, the undoped  $Al_2O_3$  film was studied, which was reactively sputtered from a 100 mm diameter Al target with 99.999% purity. The process pressure was set at the standard 3 mTorr level, and was mainly controlled by the argon flow rate. Oxygen was introduced into the sputtering chamber using a separate mass flow controller (MFC), until the bias voltage on the aluminum target started to drop significantly. An RF power of 400 W yielded a bias voltage of ~210 V across the Al target. The O<sub>2</sub> flow had to be regularly adjusted to stabilize this bias voltage, since the bias provides a direct measure of oxidization of the target surface. The O<sub>2</sub> flow remained below 4 sccm at all times, whereas the Ar flow was automatically adjusted around 60 sccm to maintain the 3 mTorr process pressure.

Al<sub>2</sub>O<sub>3</sub> films with the lowest optical losses are obtained at 250 °C (Fig. 1a) and a substrate bias of 90 W (Fig. 1b). The increase in loss at lower temperatures can be explained by insufficient surface mobility. On the other hand, at temperatures greater than 300 °C, increased loss is attributed to the tendency of the oxide to become polycrystalline with the energy provided by the increased temperature and substrate bias. In order to produce Al<sub>2</sub>O<sub>3</sub> doped with  $\text{Er}^{3+}$ , an Er target was co-sputtered at ~35 W. Using prism coupling measurements, the absorption losses are characterized at a number of wavelengths around 980 nm (Fig. 1c), and 1550 nm (Fig. 1d). Linear fits to the propagation losses show that concentrations on the order of  $1 \times 10^{20} \text{ cm}^{-3}$ , and a background loss of <0.1 dB/cm can be reliably achieved (Fig. 1e).

### 3. Laser Design and Characterization

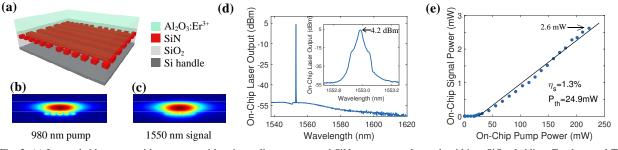

Using the new low-temperature  $Al_2O_3:Er^{3+}$  as a gain medium, a quarter-phase-shifted distributed feedback (DFB) laser with an inverted ridge waveguide of 200 nm thick SiN layer was designed. First, the SiN layer and top 200 nm thick SiO<sub>2</sub> cladding were fabricated in a standard 300 mm CMOS line. Then, the gain medium was deposited as a back end process, without the need for any subsequent etching (Fig. 2a). For the layer height of 1.2 µm  $Al_2O_3:Er^{3+}$ , and a five segment SiN design with segment width 0.45 µm, pump and signal modal confinements in the gain medium were calculated as 84.1% and 82.8% respectively (Fig. 2b, and 2c). A pump-signal overlap of 90.3% was obtained within the gain medium. Alternating SiN segments of 0.3 µm width were used on either side of the inverted ridge waveguide with a period of 0.492 µm in order to match the Bragg condition within the C-band. A quarter phase shift was introduced in the middle of the 1.5 cm long DFB, which was optically pumped from both sides with 980 nm pump diodes. Light was coupled on and off chip using inverted facet tapers; and the emission was collected by using a wavelength division multiplexer. Under these conditions, we observed single mode lasing at 1552.98 nm, with a maximum on-chip output power of 2.62 mW using 220 mW of 980 nm on-chip pump power (Fig. 2d). The threshold and slope efficiency were 24.9 mW and 1.3% respectively (Fig. 2e). This shows that the fully CMOS-compatible DFB laser with 250 °C fabricated  $Al_2O_3:Er^{3+}$  gain medium exhibits similar performance to other integrated solid-state lasers whose gain media are fabricated at much higher temperatures.

Fig. 2. (a) Inverted ridge waveguide structure with gain medium on top, and SiN segments underneath within a SiO<sub>2</sub> cladding. Fundamental TE modes for (b) 980 nm pump and (c) 1550 nm laser showing good confinement in the gain medium. (d) Laser emission as measured by the optical spectrum analyzer with the inset showing a closeup of the lasing peak. (e) Lasing curve showing on-chip pump and signal powers.

This work was supported by DARPA under the E-PHI projects, grant no. HR0011-12-2-0007.

## 4. References

J.D.B. Bradley, et al., "Erbium-Doped Integrated Waveguide Amplifiers and Lasers," Laser & Photonics Reviews 5.3 (2011), pp. 368-403.

P. Purnawirman, J. Sun, et al., "C-and L-band Erbium-Doped Waveguide Lasers with Wafer-Scale Silicon Nitride Cavities," Optics Letters 38.11 (2013), pp. 1760-1762.

[3] C.M. Sorace-Agaskar, et al., "Integrated Mode-Locked Lasers in a CMOS-Compatible Silicon Photonic Platform," CLEO, 2015, SM2I-5.

[4] K. Wörhoff, et al., "Reliable Low-Cost Fabrication of Low-Loss Waveguides with 5.4-dB Optical Gain," Quantum Electronics, IEEE Journal of 45.5 (2009), pp. 454-461.

[5] S. Sedky, et al., "Experimental determination of the maximum post-process annealing temperature for standard CMOS wafers," Electron Devices, IEEE Transactions on 48.2 (2001), pp. 377-385.

[6] H. Takeuchi, A. Wung, X. Sun, R.T. Howe, and T.-J. King, "Thermal budget limits of quarter-micrometer foundry CMOS for post-processing MEMS devices," Electron Devices, IEEE Transactions on 52, no. 9 (2005), pp. 2081-2086.